Что-то не так?

Пожалуйста, отключите Adblock.

Портал QRZ.RU существует только за счет рекламы, поэтому мы были бы Вам благодарны если Вы внесете сайт в список исключений. Мы стараемся размещать только релевантную рекламу, которая будет интересна не только рекламодателям, но и нашим читателям. Отключив Adblock, вы поможете не только нам, но и себе. Спасибо.

Как добавить наш сайт в исключения AdBlockРеклама

Дешифратор кодово-импульсных команд

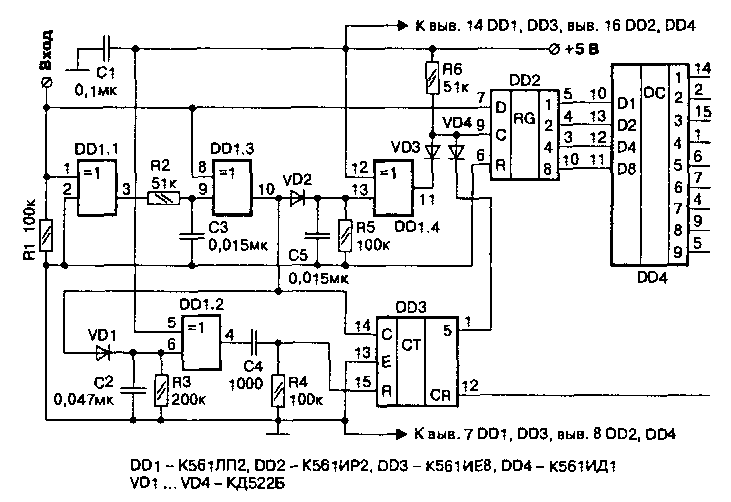

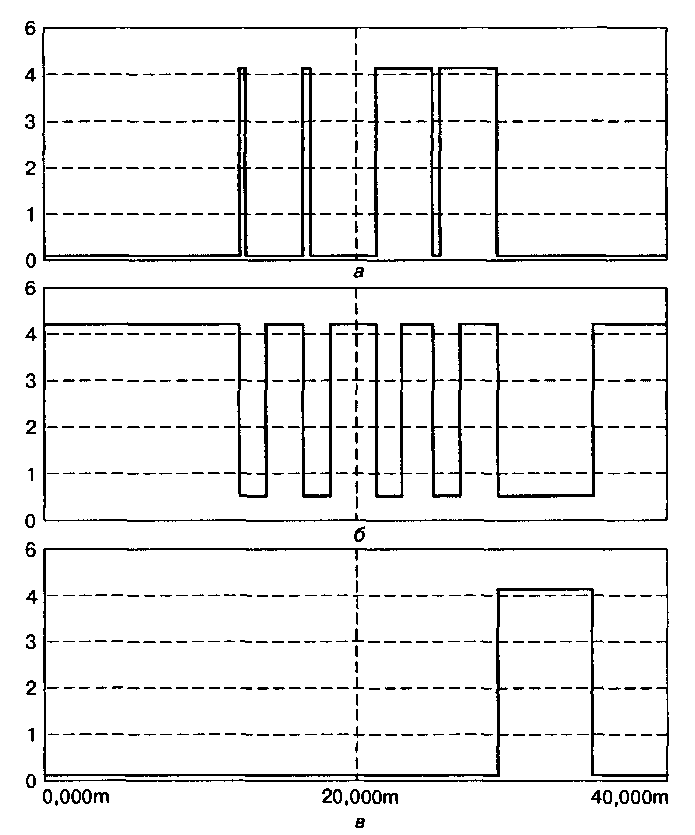

Сигнал с выхода приемника, имеющий вид, изображенный на рис. 2, а, поступает на вход дешифратора. Для примера закодировано число 3. На элементах DD1.1, DD1.3 собрана схема восстановления тактовых импульсов, которые, напомним, соответствуют по времени границам разрядных интервалов.

Рис. 1. Принципиальная схема дешифратора

Выделенные тактовые импульсы подаются на схему формирования импульсов записи, реализованную на элементах VD2, С5, R5, DDI.4. Выходной сигнал этого узла приведен на рис. 2 б. Положительные перепады, как видно, располагаются внутри разрядных интервалов.

Этими перепадами, поступающими на вход записи сдвигающего регистра DD2, производится последовательная запись информации с входа «D» микросхемы, куда подан сигнал с выхода приемника (рис. 2, а). По окончании четвертого такта записи на выходах регистра DD2 сформировано двоичное число, соответствующее номеру переданной команды. Дешифратор DD4 преобразует это двоичное число в единичный уровень на соответствующем своем выходе. В рассматриваемом примере это вывод 15.

Часть схемы, реализованная на элементах DD1.2 и DD3, обеспечивает формирование импульса разрешения считывания команды (рис. 2, в), который появляется на выходе счетчика DD3 только после окончания записи в регистр всех четырех разрядов поступившей кодовой посылки. Для нормальной работы исполнительных устройств выходы 1—9 дешифратора должны быть подключены к схемам «И-НЕ» точно так же, как это сделано в предыдущем варианте дешифратора (рис. 6.4). Импульс разрешения считывания команды (вывод 12 DD3 на рис. 6.6) необходимо подать на соединенные вместе входы элементов «И-НЕ».

Рис. 2. Принцип дешифрации команды

Если в пришедшей кодовой посылке в младшем разряде записана единица, то схема формирования импульсов записи вырабатывает один лишний импульс. Чтобы не происходило сдвига декодируемого числа на один лишний такт, прохождение пятого импульса записи на вход регистра блокируется схемой монтажного «И», собранной на элементах VD3, VD4, R6. Сигнал управления блокировкой формируется на выводе 1 элемента DD3 путем подсчета поступивших на вход импульсов записи.

Если предполагается использовать команды с запоминанием, то входы сброса «R» триггеров DD7, DD8 необходимо соединить с корпусом.