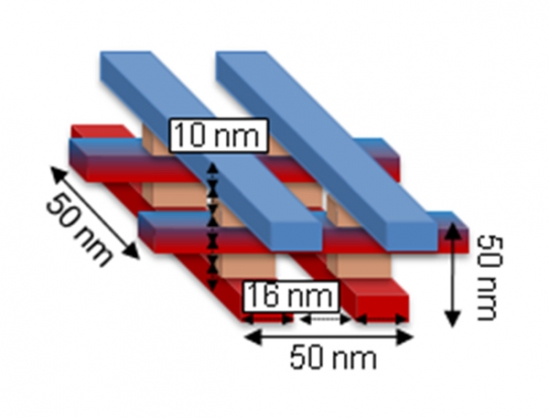

Группа инженеров из Калифорнийского университета в Санта-Барбаре разработала структуру наноразмерного функционального блока для вычислительных устройств и представила ее в рамках конкурса Feynman Grand Prize. В этом блоке, который является 8-разрядным сумматором, используется достаточно нетрадиционный вид логики, а сам блок может быть упакован в объем куба, размером 50 на 50 и 50 нанометров. К сожалению, изготовление такого блока в настоящее время невозможно в силу отсутствия соответствующих технологий, но скорость развития последних позволяет надеяться, что нечто подобное сможет стать реальностью уже в самом ближайшем будущем.

"Нам удалось разработать принципиально новый подход к проектированию схем на базе логики совершенно нового типа" - рассказывает Дмитрий Струков, профессор информатики Калифорнийского университета, - "Более того, мы не только разработали новый тип логики, но и "упаковали" электронную схему в трех измерениях, что позволило оптимизировать структуру и кардинально уменьшить ее размеры".

В основе нового типа вычислительной логики (material implication logic) лежат мемристоры, электронные компоненты, сопротивление которых зависит от величины протекавшего через них ранее электрического тока. В отличие от традиционной логики, где логические операции и хранение данных выполняются различными функциональными модулями, в новой логике эти две функции совмещены в пределах одного и того же блока. Такой подход позволяет снизить количество элементов модуля вычислительного устройства, уменьшить занимаемое им пространство и количество потребляемой энергии. Кроме этого, результат работы блока хранится в нем же и сохраняется при отключении напряжения питания в силу энергонезависимой природы мемристоров.

"К сожалению, разработанная нами технология еще слишком нова для того, чтобы говорить о ее практическом применении" - рассказывает Дмитрий Струков, который работал в свое время в технологической лаборатории компании Hewlett Packard и занимался исследованиями мемристоров, - "Нам предстоит проделать еще много работы для того, чтобы увеличить надежность новой логики, что позволит создавать не только отдельные узлы, но и большие интегральные чипы, внутри которых электронные схемы будут упакованы в десятки, сотни или тысячи слоев".

316

316